Maximizing EOS and ESD immunity in high-performance serial buses

By Burke Henehan, Texas Instruments Inc.

February 1, 2007

정전기 문제로부터 제품을 보호하는 것은 마술이다 ? 전혀 그렇지 않다 . 문제를 해결하기 위한 다층적 전략은 제품의 내성을 극대화하고 , 부품 비용과 프로젝트 일정에 미치는 영향을 최소화 한다 .

전기적 과부하 (EOS, electrical overstress) 및 정전기 방전 (ESD, electrostatic discharge) 은 반도체 장애의 주된 요인이다. 흔히 EOS 를 탓하지만, 때로는 ESD 가 EOS 를 수반하기도 한다. 어셈블리 기계가 부품을 손상시켰는지. 취급 절차에 적절한 ESD 예방 조치가 취해졌는지. 테스트 기기가 부품에 무언가를 가하지는 않았는지. 최종 사용자가 카펫 위에서 케이블을 연결하려 컴퓨터 후면의 커넥터를 찾느라 부품을 손상시켰는지 등 장애의 원인을 파악하는 것은 상당히 난해한 문제이다. 이 어려운 작업을 겪지 않으려면, 미리 장애를 예방하여 검출 작업을 최소화하는 것이 최선책이다. 이 글에서는 PC 보드의 ESD 및 EOS 내성을 극대화시키는 방법을 제시할 것이다.

ESD 는 제품에 닿아 반도체를 손상시킬 수 있는 일종의 외부 고전압 현상이다. 일반적으로 방전은 전자 현미경으로 세밀하게 스캔해야만 검출할 수 있는 절연 장애, 내부 보호 다이오드를 통한 누설 경로, 전력 레일에서 장치의 용해 홀 (melt hole) 로 전도를 발생시키는 단락 회로 등 여러 가지 요인들에 의해 발생되는 흔한 현상이다. 이러한 원인들로 인해 EOS 문제는 한 가지의 방법만으로는 해결될 수 없다.

EOS 방지는 중세 고성 건축가들의 심층적인 방어 개념과 아주 유사하다. 첫째, ESD 에너지가 유입되는 것을 차단한다.( 적의 침입을 차단 ) 둘째, 유입되는 에너지를 분산시킨다.( 적을 위태롭게 하기 ) 셋째, 유입되는 에너지에 대항해 반도체에 내성을 부여한다.( 갑옷 입히기 )

다음은 FireWire, USB, PCIe(Peripheral Component Interconnect Express) 와 같은 고속 직렬 버스에 대해 권장하는 사항이다. 섀시 (Chassis) 의 홀은 ESD 의 유입점이 될 수 있다는 것에 유의해야 한다. 고속 직렬 버스는 문제점이 아니라, 오히려 해결책일 수도 있다. 다수의 외부 연결을 결합시킴으로써 단일 직렬 버스 연결은 ESD 의 유입점을 제거할 수 있다. 이는 성으로 진입하는 유일한 문을 방어하는 것과 같은 이치다.

적의 침입 차단

첫째, 가능하다면 ESD 에너지가 반도체로 유입되지 않도록 해야 한다. 이에 가장 좋은 방법은 페러데이 케이지 (Faraday cage) 를 이용하는 것이다. 섀시 접지는 내부 전자 부품을 완전히 감싸고 있으며, 녹색 선이나 접지에 연결되어 있다. 좋은 예로 내부의 전자 부품을 감싸고 있는 전도 함체의 일종인 PC 의 금속 타워 케이스를 들 수 있다. 고속 직렬 버스는 전기 신호가 유입될 수 있는 커넥터를 장착하기 위해 홀을 연속 전도면에 필요로 한다. 제대로 설계된 직렬 버스는 신호 도체 주변이 완전히 외부와 차단되어 있으며, PC 보드 커넥터가 금속으로 차단되어 있다. 전체 차단에서 PC 보드 커넥터 차단까지 낮은 임피던스 연결이 이루어져 있고, PC 보드 커넥터와 섀시 접지를 결합한다면 연결된 장비 함체의 교접 커넥터를 거치는 이러한 연결들은 케이블 차단의 커넥터를 거친 한 장비의 금속 함체에서 유사 연속 전도면을 이룬다. 유사하다는 것은 금속 상자에 커넥터가 돌출되는 홀이 있기 때문이다. 이 공극을 통해 ESD 에너지가 유입될 수 있다. 다행히, 일부 장치들은 커넥터에서 함체 전도면까지 접촉이 이루어지도록 스프링 작용을 이용한다. 이러한 장치들의 수직 대각 접선은 커넥터가 돌출되는 함체와 접촉하고, 수평인 접선은 PC 보드 커넥터와 접촉하여 보드의 섀시 접지 또는 모두를 연결한다.

이 구조는 커넥터 쉘에서 섀시 접지까지의 연결을 짧게 하고, 함체에 돌출되는 커넥터 주변의 슬롯 안테나 길이를 줄여 ESD 와 EMI( 전자기파 간섭 ) 를 완화시킨다. 이 배치를 성의 경우에 빗대어 생각해 보자. 페러데이 케이지는 성벽이고, 커넥터 홀은 성문이라 생각하면 쉽다. 성벽으로 사방을 둘러싸고 있으며, 성문을 뚫을 수 없는 한 내부의 사람들은 안전하게 된다.

제품이 전도 함체가 없는 경우라면, 두 가지의 선택 방법이 있다. 유입되는 에너지를 소산시키거나 ( 적을 위태롭게 하기 ), 또는 ESD 에너지를 최대 전도체로 누락시켜 시간이 지남에 따라 유출되게 하는 것이다. 최대 도체로 누락 시킬 시, 도체가 지나가는 곳마다 ESD 전압이 전달되어, 다른 도체나 반도체 장치에 심각한 아크를 일으킬 수 있는 단점이 있다. 또한 전기장이 다른 반도체 장치들을 교란시킬 수도 있다. 이러한 바람직하지 못한 가능성을 설계상에서 최소화시킬 수 있다면, 최대 도체로 누락시키는 것이 더 적당한 옵션이 될 것이다.

적을 위태롭게 하기

비록 함체가 전도성을 가지고 있을지라도, ESD 는 들어갈 길을 찾을 수도 있다. 이 교활한 성질 때문에, 심층적인 방어가 필요한 것이다. 두 번째 층의 목표는 유입되는 에너지를 소산시키는 것이다. 즉, 성문을 통과하는 적들을 위태롭게 만드는 것이다. 두 번째 계층은 성의 외벽과 두 번째 벽 사이에 있는 치명적인 공간으로 생각하면 된다. 성에는 일반적으로 두 문 사이에 집중 포화를 위해 활을 쏘는 구멍이 마련된 통로가 있다. 성을 방어하는 군사들은 이 통로에서 끓는 기름을 침입자들에게 퍼붓는다. 첫 번째 벽 ( 페러데이 케이지 ) 를 통과한 적들은 두 번째 벽을 공격하기에 앞서 이 치명적인 공간에서 살아 남아야만 한다. 제품의 경우 이 단계에서는 가능한 한 많은 에너지를 소산시켜, 반도체에 이르는 에너지를 최소화시켜야 한다.

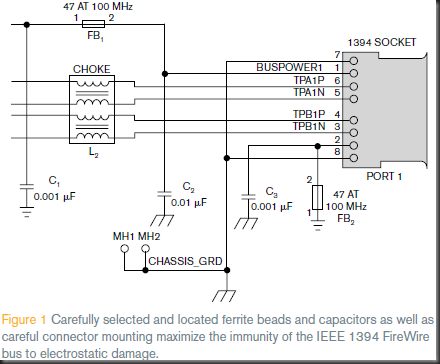

FireWire, USB, 케이블 버전의 PCIe 의 경우, 한 쌍의 반도체가 dc 케이블 전력을 공급하며 케이블 전력 복구 경로를 제공한다. 이 도체들을 엄격하게 필터링하면 ESD 가 반도체에 유입되는 것을 방지할 수 있다. 일부를 개조하면 EMI 가 유출되는 것도 방지할 수가 있다. 설계자가 스프링 메커니즘으로 섀시 접지로 연결된 커넥터의 도체 쉘을 단락 시켰다고 가정하고, 전력 연결을 살펴 보자. 고주파 ESD 의 경우, 전력 및 접지 연결 ( Figure 1 의 C 1 및 C 2 ) 의 커넥터에 가능한 한 근접하도록 커패시터를 섀시 접지에 설치할 수 있다. 하지만, IEC( 국제 전기기술 위원회 ) 의 ESD 테스트 정의에서는 테스트 전압 (V) 에 대해 150pF(C) 로 충전된 커패시터를 사용한다. 총 전하 (Q) 는 변하지 않으므로, 이 전압을 커패시터 정격 전압 50V 미만으로 줄이려면, 보호 커패시터의 값은 약 0.033μF 이어야 한다. (C=Q/V, 따라서 V=Q/C) 0.01μF 커패시터는 이 애플리케이션에서 2kV 테스트 레벨에서 작동한다. 충분히 높은 전압의 커패시터를 사용해야 하며, 전압 클램프 ( 제너 다이오드 등 ) 로 커패시터를 보호하거나, 또는 이를 고전압 TVS( 과도 전압 억제기 ) 기기로 대체해야 한다. 이러한 연결들은 전력과 접지를 위한 것이므로, 그 연결들 사이에 대형 커패시터를 설치하는 것은 문제되지 않는다.

Figure 1 의 회로는 무극성 커패시터를 사용하고 있다. 불행히 이 두 가지 예들의 커패시터 값은 비교적 낮은 편이다. 이 접근 방식은 ESD 에너지를 섀시 접지로 누락 시키기 위한 낮은 임피던스 경로를 허용한다. 비록 에너지 전부를 포착하지는 못하지만, 도움이 되기 때문에 충분할 만큼 포착한다. 다른 경로 임피던스에 비해, 커패시터의 임피던스는 커패시터에 전달된 에너지의 양을 측정하여 전력 연결과 직렬의 또 다른 보호 요소, 페라이트 비드 (ferrite bead) FB 1 으로 유도한다. 페라이트는 고주파 신호에 대한 내성을 가지고 있다. 보다 높은 주파수에서 비드의 임피던스는 커패시터의 임피던스보다 높다. 고주파 에지는 ESD 중에서 가장 크게 손상을 입히는 요소로, 커패시터와 페라이트의 조합으로 에지들을 제거할 수 있다.

또, 회로를 효과적인 EMI 필터로 만들 수도 있다. EMI 필터는 ESD 필터와 정반대로, ESD 필터는 에너지의 유입을 방지하려 하고, EMI 필터는 에너지를 유입하려 한다. EMI 의 경우, 페라이트 비드에 인접한 커패시터 C 3 은 섀시 접지가 아닌 송수신기와 동일한 접지에 연결된다. 이는 에너지를 송수신기 칩으로 되돌려 보내는 것이다. 구성도에서 보면, 이 배열은 커패시터가 다리를 이루고 상부에 페라이트가 있는 파이 필터와 유사해 보인다. 레이아웃을 보자. 이는 매우 중요한 것으로, ESD 를 제거하려면 ESD 커패시터는 ESD 의 소스인 커넥터에 가능한 한 인접해야 한다. 그러나 EMI 커패시터는 EMI 의 소스인 송수신기 칩에 가능한 한 인접해야 한다. 그러므로 보다 문제를 발생시키는 쪽에 가깝게 페라이트를 위치시켜야 할 것이다. ESD 가 더 큰 문제라면 커넥터에 가까이, 또는 송수신기의 EMI 가 더 심각하다면 송수신기에 가까이 비드를 위치시켜야 한다. 결정을 내릴만한 충분한 정보가 없다면, 페라이트를 커넥터에 가까이 위치시켜야 한다. 이는 여러 소스로부터의 EMI 가 시스템에서 유출되는 것을 방지하며, ESD 에 의한 손상을 최대한 방지한다.

교묘한 접지 연결

접지 연결은 훨씬 더 어렵다. FireWire 와 USB 모두 낮은 임피던스 복귀 경로, 즉 케이블의 접지 도선을 통과하는 접지 복구 경로를 필요로 하는 공통 모드 신호 방식을 사용한다. 때문에, ESD/EMI 요건을 충족시킬 다른 대안이 없는 한 페라이트 비드를 접지 도선과 직렬로 배치해서는 안된다. 비드를 꼭 사용해야 할 경우, 비드를 광범위하게 테스트하여 작동 여부를 확인해야 한다. 그러나 가능한 한 커넥터에 인접하게, 신호 접지에서 섀시 접지로 커패시터를 연결하면 ESD 억제에 도움이 된다. 이 커패시터는 전류 분할기를 이루어, 대부분의 전류가 신호 접지 연결을 통과하게 된다. 그러나 일부는 섀시 접지에 연결된 커패시터를 통과하지만, 다행히도 큰 차이가 있다.

가장 어려운 점은 동등하게 다루어야 하는 고속 신호 라인이다. 라인들 중, 어느 하나에 어떤 조치를 취한다면 다른 쌍의 두 라인 모두에 취해야 한다. 적절한 방법은 일반적으로 사용하고자 하는 기술에 대한 공통 모드 초크이다. 공통 모드 초크는 두 도체에 공통인 신호에 대해 높은 임피던스를 보여주며 차동 신호들을 통과시킨다. ESD 와 EMI 모두 공통 모드 현상을 보이므로, 이 방법은 두 가지 모두에서 잘 작용한다. 그런데, 부품 배치에는 교환조건이 뒤따른다. 커넥터에 인접하여 초크를 배치하면, ESD 에 상당한 영향을 미친다. 송수신기 가까이에 위치시키면 송수신기 EMI 를 가장 크게 완화시킨다. 페라이트의 경우와 같은 이유로, 송수신기 EMI 가 초크를 추가해야 하는 중요한 까닭이 없는 한, 초크를 커넥터에 인접해 배치해야 한다. 두 차동 쌍을 갖춘 FireWire 의 경우, 공통 코어를 갖춘 단일 장치는 훨씬 작은 PC 보드 공간을 차지한다. 그러나, 각 쌍에 대하여 별도의 초크를 사용하면 두 쌍 간의 누화가 줄게 된다.

이러한 것들에 관해 여러 가지 생길 수 있는 문제점을 고려하고 주의를 기울여야 한다. 우선, 커패시터를 고속, 연선 신호 라인에 두지 않아야 한다. 주파수 때문에 몇 피코패럿 (picofarad) 이상의 정전용량이 신호 무결성을 불러온다. 테스트 제품이 처음에는 잘 작동하는 것처럼 보일지라도, 비트 오류율이 높을 수 있다. 또한 사용하고 있는 기술이 분명히 증명된 경우를 제외하고서는 공통 모드 초크를 사용하지 말아야 한다. FireWire 버전 A(IEEE 1394a) 는 공통 모드 신호방식 메커니즘을 사용하여 패킷 전송속도를 측정한다. 신호 라인 상의 공통 모드 초크가 이 공통 모드 신호를 통과시키지 않을 경우에는 98.304Mbps 패킷 전송이 가능한 경우라도, 더 빠른 속도의 패킷 전송은 불가능할 것이다.

양면 보드 또한 사용하지 말아야 한다. 직렬 버스들이 작동하는 주파수에서, 방출 신호 경로와 접지 복구 경로가 포함되어 있는 루프 임피던스는 신호 무결성과 발생한 EMI 의 양을 측정한다. 트레이스 하에 견고한 접지 층이 있고, 이 트레이스들에 비아 (via) 를 사용하지 않으면 레이아웃 작업은 한결 수월해 질것이다. 비아를 사용하면 신호 무결성에 손상을 주며, 이미지 평면을 연결하여 신호 경로 루프 면적을 최소화시켜야 하므로, 레이아웃이 매우 복잡해지게 된다. 송수신기에서 커넥터 핀으로 연결된 연선 신호 라인 하에, 견고한 접지 층을 갖춘 4 층 보드를 사용해야 한다. 커넥터 쉘에 연결되어 섀시 접지에 연결되는 부품의 연결 점을 제공하는 섀시 접지 층에는 견고한 플러드 (flood) 를 사용해야 한다. 그러한 보드의 레이아웃 시, 섀시 접지 플러드의 형상을 단순화시키는 것보다 신호 라인의 전체 길이 하에 견고한 신호 접지 층을 두는 것을 더욱 우선해야 한다.

갑옷 입히기

ESD 가 흩어진 방어막을 통과한다면, 적군들이 아성에 침입한 것과 같은 상황이 된다. 설치한 방어막을 넘어 온 에너지로부터 장치들을 보호해야만 한다. 모든 반도체 장치들에는 어떤 종류의 ESD 보호 기능이 내장되어 있다. 데이터 시트를 확인해 보자. 그러나 대부분의 경우 PC 보드에서 더 많은 조치를 취할 수 있다. 최종 목표는 반도체의 기능을 방해하는 모든 것들을 막아내는 것이다. 첫 번째로 점검해야 할 것은 리셋 핀이다. 이 핀들이 우발적으로 상태를 바꾸지 않도록 만들어야 한다. 대부분 그렇듯이 리셋 핀의 한계치가 접지 기준이라면, 리셋 핀에서 접지로 커패시터를 배치해야 한다. 커패시터는 리셋 핀이 접지 바운스 중, 상태가 변하지 않도록 하는데 도움이 된다. 이 경우, 하나의 이벤트가 접지 기준의 레벨을 변화시킨다. 변화가 상당히 클 경우에는, 반도체는 리셋을 실행시킬 수 있다. 짧은 접지 바운스 중, 리셋 핀에서 접지로 연결된 커패시터는 핀과 접지 간의 공칭 전압을 일정하게 유지하는데 도움이 된다. 보다 긴 이벤트 동안, 전압 변화를 허용하는 커패시터의 전하 유출은 한계치 초과점이다. 때문에 커패시터의 값을 가능한 한 크게 해야 한다. 리셋 핀이 대부분 dc 신호일 경우, 1μF 이상의 커패시터를 배치해야 한다. 구동 신호에 심한 부하를 주거나 주파수를 심하게 제한하는 경우, 낮은 값의 커패시터를 사용해야 하나, 이 경우에는 가급적 큰 값을 사용하는 것이 좋다. 동일한 논리를 반도체를 손상시킬 수 있는 모든 입력에 적용한다. FireWire 물리 계층의 경우, 리셋 및 LPS( 링크 - 전력 - 상태 ) 핀에 특별한 주의를 기울여야 한다.

ESD 공격에 접할 수 있는 기타 핀의 경우, 반도체와 ESD 공격 간에 아주 작은 저항만을 추가하더라도 반도체 보호에 도움이 된다. 예를 들어, 심각한 영향을 미치지 않도록 반도체에 최대한 가까이 근접하여 10Ω 레지스터를 신호와 직렬로 배치하면, ESD 내성이 증가한다. 이러한 요소들을 추가하는 것은 병사들에게 갑옷을 입히는 것에 비유할 수 있다. 갑옷이나 쇠사슬을 두른 기사들이 천으로 된 옷을 입은 기사들 보다 전투력이 훨씬 우수한 이치와 같다.

방어의 정도

이 모든 대책이 다 필요한 것일까 ? 사실 이것은 상황에 따라 다르다. 몇 개의 보드를 구축하는 경우라도 추가로 경비와 시간을 들여 가능한 한 견고하게 만들어야 한다. 제품에 고속 직렬 버스를 설계할 때, 설계 및 부품에 투자하는 경비와 시간은 최적의 위험 방지책이라고 할 수도 있다. EMI 및 ESD 영역을 점검하는 비용은 부품과 PC 보드에 부품을 배치하고, 백여 개의 보드를 구축하는데 드는 설계 시간 비용보다 훨씬 크다. ESD 및 EMI 영역의 두세 차례 사전 점검으로도 중요한 부분을 놓치는 경우가 종종 있으므로 이는 대단히 중요하다. 보드 수량이 아주 많다면, 융통성 있게 균형을 맞출 수 있다. 또한 수천 개의 보드를 구축하고 보드 당 1 달러 정도를 낮출 수 있다면, ESD 및 EMI 영역도 수 차례 점검해야 할 것이다. 당장에는 이 같은 점검이 지나치다고 여겨질 지 모르지만, 추후에는 보드 설계에서 더 많은 보호 요소들을 채택하는데 거의 비용이 들지 않는다. 비용의 절감을 위해, 특정 부품이 반드시 필요한 것이 아니라고 생각되면, 이를 부품 리스트에서 삭제하거나 보다 저렴한 0Ω 레지스터로 대체하자. 이러한 조치들은 전형적으로 초래할 수 있는 위험에 균형을 맞추는 것으로, 모든 설계자들이 해야 할 일이기도 하다.

Acknowledgements

As a senior member of the technical staff at Texas Instruments (Dallas), Burke Henehan defines audio amplifiers for mobile devices. He holds a master's degree in systems engineering from Texas Tech University (Lubbock, TX) and a bachelor's degree in electrical engineering from South Dakota School of Mines and Technology (Rapid City, SD). You can reach him at bh055@yahoo.com.

한글번역출처: http://www.ti.com/ww/kr/article/tiatc_07september_num06.html

댓글 없음:

댓글 쓰기